掃碼添加微信����,獲取更多半導(dǎo)體相關(guān)資料

硅片表面的金屬污染物可能對其上制造的半導(dǎo)體器件造成不可逆的損傷����,銅也不例外�����,它將減少少數(shù)載波壽命�,減少DRAM的刷新時間,增加反向偏置結(jié)泄漏電流�����,這會導(dǎo)致柵氧化物漏電流增加,并降低柵氧化物的擊穿電壓���,隨著設(shè)備尺寸的縮小����,這個閾值在未來可能會降低。

為了實現(xiàn)柵極氧化物完整性(GOI)�,通過斜坡電壓試驗確定缺陷密度�,與時間相關(guān)的介電擊穿是對設(shè)備保持運行時間長度的衡量標準��,因此是可靠性的衡量標準��,雖然使用了不同類型的晶圓���,不同的引入銅污染的方法����,以及不同的GOI指標��,銅的植入、背面銅污染����、化學(xué)浸漬污染和旋轉(zhuǎn)污染都被用于在門氧化之前或之后引入已知數(shù)量的銅,有時氧化物缺陷密度(D)�����,有時平均氧化物擊穿場(Ebd)被報道為銅對GOI影響的測量方法���,缺陷密度的含義在所有來源中并不一致�,因為用于確定擊穿的閾值在8MV/cm和12MV/cm之間變化,平均擊穿場的含義在所有源中都不是均勻的�,因為已經(jīng)使用了不同的電容器區(qū)域來確定它們��。

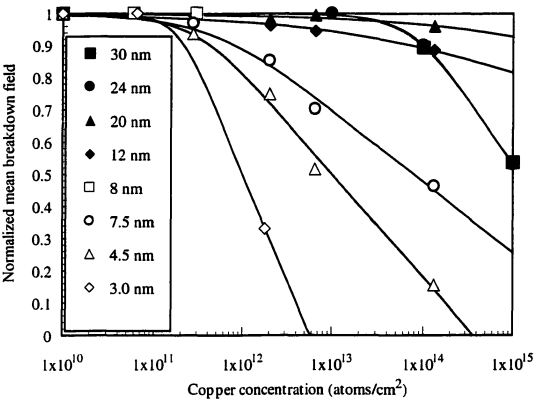

從圖中可以看出��,銅濃度有一個閾值��,低于這個閾值��,銅對平均擊穿場沒有可檢測到的影響��,如果銅濃度超過這個閾值����,平均擊穿場開始下降���。一般來說�,氧化物越薄���,它下降得越快,這意味著保持加工條件尤其重要�,以便在氧化物厚度較小時不超過允許的銅濃度�,因為100種薄氧化物對產(chǎn)率的影響會更大,如果通過植入引入高劑量的銅���,平均擊穿場也會迅速降低�,這可能是因為高劑量植入造成的損傷允許在(損傷的)表面附近有更多的銅沉淀��。

利用透射電子顯微鏡(TEM)���,已經(jīng)證明銅污染通過沉淀影響氧化物缺陷,在氧化溫度上升時�����,銅可能很容易擴散到硅中�����,氧化前只有一小部分銅被并入氧化物中�����,銅很容易在硅中沉淀�,因為它在硅中具有很高的擴散系數(shù),并且其固體溶解度與溫度密切依賴���,為了發(fā)生沉淀�,也必須存在成核位點����,這些缺陷既可以是晶格缺陷��,也可以是通過均勻成核而形成的缺陷。

由于高頻溶液中的銅沉積與硅溶解同時發(fā)生���,因此可能會發(fā)生硅粗糙化,這反過來又會影響生長在這個表面上的氧化物的可靠性����,晶翅片(Cz型)在SPM和稀釋的高頻浴中清洗,然后將它們放在受銅污染的稀釋高頻浴中污染1分鐘���。染的APM溶液的銅污染達到一個穩(wěn)定的濃度,可以用一個簡單的吸附和蝕刻模型充分描述���,如果在硅中存在足夠多的量,銅可以在Si/SiOi界面上沉淀�����,導(dǎo)致巨大的產(chǎn)率損失��,銅開始以這種方式影響產(chǎn)率時的閾值濃度取決于氧化物的厚度���,對于薄于12納米的氧化物,閾值濃度在2xlO“原子/cm”附近����。

經(jīng)過高溫氧化的晶翅片對隨后的銅污染不那么敏感��,很可能是硅自身間隙的存在導(dǎo)致沉淀的核化和生長更加困難�,或者它驅(qū)動銅進入取代位點�����。在柵氧化之前��,硅表面的銅污染導(dǎo)致面積和場重疊成分的屈服損失��,這是在野外重疊邊緣的銅吸收和沉淀的結(jié)果���。在介質(zhì)電場中���,可以看到一個大的與周邊相關(guān)的柵極氧化物泄漏電流分量���,這導(dǎo)致了現(xiàn)場重疊邊緣的可靠性問題,這被Qbd測量證實�,結(jié)漏電流還具有面積和周界分量,周長分量比預(yù)期的面積要大得多�����,因為銅的輪廓在表面附近達到峰值�,由于當電路擴展到更小的尺寸時,器件的周長變得相對重要�����,周長產(chǎn)率和可靠性問題在高密度電路中占主導(dǎo)地位�����,因為銅被保留在場重疊邊緣和表面附近,即使在低濃度下�����,它仍然是一個問題污染物。

研究發(fā)現(xiàn)����,從受污染的HF溶液中沉積的非常低水平的銅會導(dǎo)致氧化物中高密度的凸起�����,研究表明����,結(jié)果表明����,這些凸起不是電短路����,相反這些凸起的氧化物比周圍的氧化物厚,SIANTRS投影的MOSFET柵極下凸點引起的電容變化將導(dǎo)致閾值電壓偏移����,這對于具有0.13微米特征尺寸且更小的設(shè)備技術(shù)來說是不可接受的���。